Received July 23, 2021, accepted September 13, 2021, date of publication September 23, 2021, date of current version October 5, 2021.

Digital Object Identifier 10.1109/ACCESS.2021.3115243

# ALOHA: A Unified Platform-Aware Evaluation Method for CNNs Execution on Heterogeneous Systems at the Edge

PAOLA BUSIA<sup>®</sup><sup>1</sup>, SVETLANA MINAKOVA<sup>2</sup>, TODOR STEFANOV<sup>®</sup><sup>2</sup>, (Member, IEEE), LUIGI RAFFO<sup>®</sup><sup>1</sup>, AND PAOLO MELONI<sup>®</sup><sup>1</sup>, (Member, IEEE)

<sup>1</sup>DIEE, University of Cagliari, 09123 Cagliari, Italy

<sup>2</sup>LIACS, Leiden University, 2333 CA Leiden, The Netherlands

Corresponding author: Paolo Meloni (paolo.meloni@unica.it)

This work was supported by the European Union's Horizon 2020 Research and Innovation Program under Grant 780788.

**ABSTRACT** CNN design and deployment on embedded edge-processing systems is an error-prone and effort-hungry process, that poses the need for accurate and effective automated assisting tools. In such tools, pre-evaluating the platform-aware CNN metrics such as latency, energy cost, and throughput is a key requirement for successfully reaching the implementation goals imposed by use-case constraints. Especially when more complex parallel and heterogeneous computing platforms are considered, currently utilized estimation methods are inaccurate or require a lot of characterization experiments and efforts. In this paper, we propose an alternative method, designed to be flexible, easy to use, and accurate at the same time. Considering a modular platform and execution model that adequately describes the details of the platform and the scheduling of different CNN operators on different platform processing elements, our method captures precisely operations and data transfers and their deployment on computing and communication resources, significantly improving the evaluation accuracy. We have tested our method on more than 2000 CNN layers, targeting an FPGA-based accelerator and a GPU platform as reference example architectures. Results have shown that our evaluation method increases the estimation precision by up to  $5 \times$  for execution time, and by 2× for energy, compared to other widely used analytical methods. Moreover, we assessed the impact of the improved platform-awareness on a set of neural architecture search experiments, targeting both hardware platforms, and enforcing 2 sets of latency constraints, performing 5 trials on each search space, for a total number of 20 experiments. The predictability is improved by 4×, reaching, with respect to alternatives, selection results clearly more similar to those obtained with on-hardware measurements.

**INDEX TERMS** Convolutional neural networks, edge-computing, platform awareness.

## I. INTRODUCTION

Convolutional Neural Networks (CNNs) [1] are biologically inspired graph computational models, characterized by a large number of parameters and a high degree of parallelism. Due to their ability to handle large, unstructured data, CNNs are widely used to perform tasks such as image and video recognition, image segmentation, natural language processing, and many others [2]. Nowadays, CNNs are the backbone of many applications, such as navigation in self-driving cars [3], medical image recognition [4], surveillance [5],

The associate editor coordinating the review of this manuscript and approving it for publication was Fan Zhang.

and others [2]. Due to the intense computation workload associated with their execution, CNNs often require, especially when operating at the edge, to exploit acceleration on dedicated processing elements, usually heterogeneous and highly parallel. CNN inference has been ported on a wide spectrum of platforms: from high-performance GPU clusters to embedded systems and mobile devices [6], [7]. Nevertheless, the landscape of CNN-enabling cores and processors in literature is increasingly vast: the majority of silicon vendors and market actors are proposing new accelerator or processor architectures designed to improve the efficiency of CNN execution ([8]–[12]). Rounding up the numbers, the main three classes of processing elements exploited for this kind

of workload are CPUs, GPUs, and dedicated processing elements. Understanding the execution of a specific CNN architecture on such complex processing systems, before the actual deployment, is a key need during several design steps: e.g. during target platform selection, CNN topology definition also referred to as Neural Architecture Search (NAS), task-to-core mapping optimization, code-level optimization. Most of these steps are time-consuming activities requiring sufficient expertise in the field of Deep Learning (DL) [2], to be performed manually.

Thus, automated design flows and tools are appearing in the literature, to assist non-experts in such challenging tasks.

However, most tools reported in the literature have a limited degree of platform awareness: they fail to capture the effect of potential design choices on the performance metrics achievable by a CNN architecture under consideration executed on a target computing platform, especially when dealing with more complex processing systems, endowed with accelerators, highly-parallel processors and/or GPUs. Estimation methods implemented in these tools are inaccurate ([13]–[15]), or not sufficiently general ([16]–[23]), or require a lot of design experiments and modeling skills to be used ([24]–[26]).

A common unified method that solves all these issues, implementing platform-awareness within automated tools for CNN design, is still missing.

Therefore, in this paper, we propose the ALOHA<sup>1</sup> method for the evaluation of platform-dependent metrics of a CNN, executed on a heterogeneous platform. Our method relies on a platform-aware evaluation model, described in Section VI, designed to:

- provide realistic and accurate results: the model is capable of capturing platform-aware characteristics, such as occupancy of platform processors, exploitation of parallelism available in a platform by CNN operators, repeated data transfers occurring during CNN execution, and others;

- be flexible: the model is not dependent on any specific processing element architectural template. Characteristics that are captured in the model are abstract enough to be usable for the description of significantly different platform organizations and structures;

- be modular: one component of the model describes the

platform, while a second part describes the deployment

strategy which is used by the implementation of CNN

layers (defined by the user or the selected library). This

improves both accuracy and re-usability because both

components can be adopted in different design cases.

- require low development effort: the model does not require benchmarking. All the information required to capture the platform and library can be easily derived

<sup>1</sup>The ALOHA project is available at https://www.aloha-h2020.eu/ and aims at developing a framework providing several tools for architecture-aware CNN exploration. This work only focuses on modeling, and it does not deal with adaptivity, pruning, and quantization themes.

from specs or a general understanding of the platform/library operation principles.

To evaluate our method, we compare the accuracy provided by our proposed method with others with a similar level of abstraction and development effort, considering two heterogeneous platforms as a reference: an open-source FPGA-based platform called NEURAghe [27] and a GPU-based Jetson TX2 platform [28]. The architectures presented in this paper are exactly chosen to represent the three classes of common processing elements in the embedded domain. JetsonTX2 is a SoC integrating CPU and GPU. NEURAghe is implemented on a SoC that integrates CPU and a CNN-dedicated processing element implemented on reconfigurable logic. Thus we believe that overall, this selection covers most of the embedded landscape.

The comparison shows that our approach significantly improves the evaluation precision. Moreover, we perform several NAS experiments, optimizing the topology of a CNN to perform classification on the CIFAR-10 dataset [29], under user-defined latency constraints and targeting the aforementioned platforms. For each exploration, we used different kinds of evaluation methods to confront candidate design points with the constraint. Comparing the NAS results obtained using our method with those obtained using other comparable models, we show that our method significantly improves predictability, bringing NAS selection very similar to the one obtained by actual on-hardware measurements.

## A. PAPER CONTRIBUTIONS

The main novel contributions in this paper can be summarized as:

- an accurate, easy to create and yet generalizable and reusable platform model and evaluation method, proposed in Section V and Section VI, suitable to implement platform-awareness in CNN design and optimization tools;

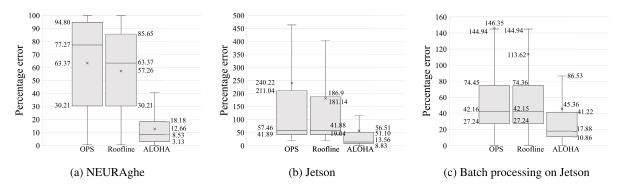

- assessment of the impact of platform-awareness on the latency estimation (Section VIII-A), reducing by 3× to 5× the average error in CNN latency estimation, compared to commonly used methods such as the Roofline model [16] and operation count, for layer-level evaluation, and by 1.6× when considering aggregated CNN-level results on multiple cores (Section VIII-D);

- assessment of the impact of platform-awareness on the energy estimation (Section VIII-B), showing a 1.9× estimation precision improvement;

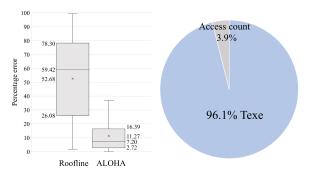

- assessment of the impact of platform-awareness on NAS (Section VIII-C), reducing thanks to the proposed method the latency and accuracy deviation from a similar NAS exploration having access to actual on-hardware measurements by a factor of 4, compared to the alternative methods examined.

## **II. RELATED WORK**

As an answer to the demand for CNN-based edge-processing, custom-developed devices and computing systems, an

| TABLE 1. | Comparison of | f methods fo | evaluation o | of platform-aware | CNN metrics. |

|----------|---------------|--------------|--------------|-------------------|--------------|

|----------|---------------|--------------|--------------|-------------------|--------------|

| Eval. method category | Methods          | Metric                      | Accuracy     | Re-usability | Modularity |  |

|-----------------------|------------------|-----------------------------|--------------|--------------|------------|--|

| OPS                   | [13]             | latency                     | low          | very         | X          |  |

| 013                   | [14]             | memory, latency, energy     | 10W          | high         | A          |  |

| Roofline              | [30]             | latency                     | low/ medium  | high         | X          |  |

| Specialized           | [23]             | latency, energy, memory     | medium/      | low          |            |  |

| analytical            | [21], [31]       | latency, energy             | high         | IOW          | X          |  |

| methods               | [19], [20], [22] | latency, energy, throughput | lingii       | medium       |            |  |

| Measurements          | [32]             | latency                     | high         | very         | X          |  |

|                       | [33]             | latency, energy             | lingii       | low          | Λ          |  |

| Look-up tables        | [34]             | latency                     | high         | low          | X          |  |

| (LUT)                 | [35]             | latency                     | high         | medium/ low  |            |  |

| ML                    | [36]             | latency, energy             | high         | very         | X          |  |

| 14117                 | [26]             | latency                     | ] ""g"       | low          | Λ          |  |

| ALOHA                 | this work        | latency, energy, throughput | medium/ high | high         | <b>√</b>   |  |

ever-increasing number of automated/assisted design tools have been recently proposed. Among such tools, some act very early in the design flow, when the processing platform and the on-platform deployment strategy are still not already selected or physically available. A key example of such early intervention is provided by Neural Architecture Search (NAS). Multi-objective NAS has been an active research topic during the last several years, and a large number of methods, capable of evaluating platform-dependent CNN metrics to assist it, have been proposed. Table 1 provides the overview and comparison of these methods, summarized into categories, listed in Column 1. Every evaluation method is supplied with a list of evaluated platform-aware metrics (Column 3). Every evaluation methods category is supplied with a list of methods belonging to it (Column 2), and characterized with: 1) the method accuracy (Column 4); 2) the method re-usability (Column 5); 3) modularity (Column 6). The method re-usability determines how sensitive the evaluation method category is to a specific CNN architecture or/and hardware platform, and determines the applicability of the evaluation method category. For example, the OPS category, shown in Row 2 of Table 1, has very high re-usability: it can be easily applied to a wide range of CNNs and hardware platforms and does not require any modifications if the range of explored CNNs or target platform is changed. In contrast to the methods from the OPS category, the methods, based on ML models, and shown in Rows 12 to 13 of Table 1, demonstrate very low re-usability. Once designed, the ML models, used in these methods, are only applicable to a specific set of explored CNNs and a specific target platform. If the target platform or set of explored CNNs changes, the ML-based models have to be designed from scratch. Low re-usability of an evaluation method might limit the use of this method or involve large design time overheads. With the rapidly increasing number and diversity of CNNs as well as platforms, used to execute the CNNs, high evaluation method re-usability is an important quality metric of the evaluation methods, used in NAS.

Modularity (Column 6) specifies whether an evaluation method accounts for the modular composition of the platform, considering the distribution of CNN layers over the processors of a heterogeneous platform as well as for a specific schedule, associated with the CNN execution. Typically the execution of a CNN, on an accelerator-based platform, involves layer-by-layer execution of a CNN and offloading of computations within every CNN layer onto a platform accelerator [2]. Such CNN execution is typical for the majority of widely used DL frameworks such as PyTorch [37] or TensorFlow [38]. However, the ongoing research in the field of Edge AI is exploring alternative, more efficient ways to execute CNNs on heterogeneous edge platforms [7]. For example, methods, proposed in papers [39]-[41], enable for better utilization of computational resources, available on the platform. The exploitation of these methods can significantly affect platform-aware CNN metrics, such as CNN throughput and energy consumption. Thus, for efficient evaluation of platform-aware metrics of a CNN, executed at the edge, evaluation methods should have means to account for such advanced CNN execution methods.

The OPS-based evaluation methods, shown in Rows 2 to 3 of Table 1, estimate the CNN latency using the number of operations (OPs) required to execute a CNN. Such evaluation methods are simple to use and are characterized by high reusability. However, the predictions provided by the ops-based evaluation methods are often inaccurate [42], [43]. Low accuracy in the evaluation methods might lead to a large margin between predicted CNN metric and real CNN metric measured when a CNN is executed on the target platform. Such a large margin is unacceptable for the design of CNN-based applications with strict resource constraints, such as self-driving cars [3] or object recognition on drones [44]. Unlike the OPS-based methods, our method provides more accurate evaluations, and thus, allows us to obtain more realistic predictions of platform-dependent CNN metrics.

The Roofline methods, shown in Row 4 of Table 1, evaluate platform-dependent metrics of a CNN, using the analytical platform-aware Roofline model [16]. These methods, in addition to the number of OPS performed by a CNN during its execution, take into account the impact of memory access on the platform-aware CNN metrics, which allows these

methods to perform more precise CNN metrics evaluation, compared to the OPS-based methods, explained above. However, as the OPS-based evaluation methods, the Roofline methods lack evaluation accuracy. In our method, we propose a novel platform-aware evaluation model, alternative to the Roofline model. Our evaluation model considers a wider range of platform-aware characteristics, and provides a more precise evaluation of platform-dependent CNN metrics, compared to the Roofline model.

Specialized analytical methods, shown in Rows 5 to 7 of Table 1, use highly detailed representations of hardware platforms to provide a precise estimation of platform-dependent CNN metrics. However, the utilization of highly specialized hardware specifications leads to narrow application and low re-usability of these methods. For example, the authors of [19]–[21] target the exploitation of a precise roofline-based model for FPGA codesign. However, the model, utilized in [19]-[21] cannot be applied to other platforms, such as CPUs-GPUs platforms. Analogously, the work in [22] explores ASICs codesign, through performance evaluation based on MAESTRO [45], which makes the evaluation method, proposed in [22], only applicable to ASICs-based platforms. With the rapidly increasing number and diversity of devices, used to execute CNNs, such high specialization significantly limits the use of these methods. In contrast to these methods, we propose an abstract high-level specification of a hardware platform, which contains many platformaware details, affecting platform-dependent metrics of CNNs, and which applies to a wide range of diverse hardware platforms. Thus, our method enables for higher applicability and re-usability, compared to the methods proposed in [19]–[21].

The measurement-based methods, Rows 8-9 of Table 1, are based on actual measures of real latency of CNNs on the target platforms. Some similar approaches, Rows 10-11 of Table 1, use measured latency values for CNN components collected in Look-up Tables (LUTs) to produce by composition the estimation of entire CNNs. These methods ensure highly precise evaluations. However, they involve a large number of measurements of specific CNNs mapped on a specific target platform, especially in the case of measurement-based methods [32], [33], or limit the range of analyzable CNNs to those composed by modules available in the LUT. Thus, these methods show very low re-usability. On the contrary, our method uses abstract platform specification and CNN description, enabling its high re-usability.

The evaluation methods, based on ML models, and shown in Rows 12 to 13 of Table 1, use trainable ML models such as neural networks or regression models, to predict the platform-dependent metrics of a CNN. However, like the measurement-based methods and LUTs, explained above, the ML methods require a large amount of platform-and CNN-specific measurements, and demonstrate very low re-usability. Unlike these methods, ours does not require platform- and CNN-specific measurements and demonstrates high re-usability.

TABLE 2. The required profiling time for the evaluation methods based on ML models is described as the sum of two major components: the time required to acquire the training data, and the time required to perform the training procedure. The Data Collection time is expressed as the product of 1) the number of samples evaluated, n\_sample, 2) their execution time on the target hardware, t, and 3) the number of times each measure is repeated to obtain an accurate value, Nava.

| Method | Data Collection time      | Training time      |

|--------|---------------------------|--------------------|

|        | $n\_sample * t * N_{avg}$ |                    |

| [25]   | 75000 * t * 5             | (300 epochs)       |

| [26]   | $80000 * t * N_{avg}$     | 1h (1000 epochs)   |

| [32]   | 90000 * t * 50            | 20min (150 epochs) |

| [36]   | $447 * 108 * t * N_{avq}$ | not specified      |

Table 2 provides an overview of the required profiling time for the highly accurate estimation methods based on ML models. All of the listed works require a significant amount of deployments and measurements: assuming the execution time of a network to be, on average, equal to 15 ms, for example, [25] would require over 1 hour of data collection, while over 18 hours are needed in [32]. This is a very soft hypothesis, as in [26] almost 2 weeks of data collection time are claimed. In some cases, the training procedure can be exploited for a wide range of targets (e.g. [36] evaluates 447 different GPU configurations, while [25] suggests training a single network for predicting performance on multiple hardware), while, in general, such procedure has to be repeated for each target platform. On the contrary, the ALOHA method does not require benchmarking.

Finally, to the best of our knowledge, our method advances the state-of-the-art combining the flexibility characteristics of analytical methods with improved accuracy. Thus, it provides results similar to measurement-based methods, without requiring intensive modeling effort. Moreover, to the best of our knowledge, this is the first work that implements modular pre-estimation, taking into account the mapping and concurrent execution of different computational kernels on different processing cores, among those available on the platform, and providing system-level performance estimation.

## III. BACKGROUND

We summarize in this section some background notions that will be widely used in the paper. In Section III-A we describe the specifics of CNN architectures. In Section III-B and III-C we briefly present the theory of the analytical methods that we compare our method with in the following sections, the OPS count and the Roofline models.

#### A. CNN COMPUTATIONAL KERNEL DESCRIPTION

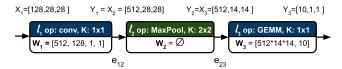

A Convolutional Neural Network (CNN) can be represented as a directed acyclic computational graph CNN(L, E) with a set of nodes L, also called layers, and a set of edges E [2]. An example of a CNN with layers  $L = \{l_1, l_2, l_3\}$  and edges  $E = \{e_{12}, e_{23}\}$  is given in Figure 1.

Every layer  $l_i \in L$  represents a part of CNN functionality. It accepts as input data  $X_i$ , provided by other CNN layers or external sources, and provides as output data  $Y_i$ . The

FIGURE 1. CNN.

layers input and output data are stored in multidimensional arrays, called tensors [2]. In this paper, the input and output data tensors have the format [T.B, T.C, T.H, T.W], where T denotes the tensor; T.B, T.C, T.H, T.W are the batch size, the number of channels, the height and the width of the tensor, respectively. Being one of the most common processing choices for embedded inference execution, and the one required by most real-time applications, we place particular focus on the processing case where the batch size is equal to 1, where T.B dimension can be omitted in the notation. To obtain the output data  $Y_i$  from the input data  $X_i$ , layer  $l_i$  moves along its input with a sliding window  $K_i$ , and applies a CNN operator op<sub>i</sub> (such as convolution, MaxPooling, GEMM, RelU etc. [2]), parameterized with weights  $W_i$ to its input data tensor  $X_i$ . We consider layer  $l_1$  in the CNN structure in Figure 1 as an example of CNN layer, with input data tensor  $X_1 = [128, 28, 28]$ , output data tensor  $Y_1 =$ [512, 28, 28], and a 2-dimensional sliding window  $K_1$  with width  $K_1.W = 1$ , and height  $K_1.H = 1$ .

Each CNN edge  $e_{ij} \in E$  specifies a data dependency between CNN layers  $l_i$  and  $l_j$ , such that layer  $l_j$  accepts as input the data tensor  $Y_i$ , produced by layer  $l_i$ . The data dependencies, specified by the CNN edges, determine the order, in which CNN layers are executed on a target platform. Typically, CNN layers are executed in sequential order, i.e., a CNN execution can be represented as |L| computational steps, where at every i-th computational step, CNN layer  $l_i \in L$  is executed.

Considering the memory footprint of current state-of-theart CNNs and the on-chip memory available in most embedded processing platforms, execution of layer  $l_i$  on a target platform typically involves:

- 1) loading of input data  $X_i$  and weights  $W_i$  of layer  $l_i$  from the global memory of the platform into the local memories of the platform processor, allocated for execution of  $l_i$ ;

- execution of the computations within the layer on the allocated platform processor;

- 3) copying of output data  $Y_i$  of layer  $l_i$  from the local memories of the allocated processor into the platform global memory;

The computations, performed within every CNN layer, are data-parallel computations, that can be represented using a set of nested loops, bound by the dimensions of tensors  $X_i$  and  $Y_i$ , as well as sliding window  $K_i$ . The nested loops enclose a simple operation, applied to the input and output data of the CNN layer. Hereinafter, we refer to such a set of nested loops as to the *computational tensor* of a CNN layer.

TABLE 3. Laver-specific computational tensor parameter.

| CNN     |     | Computational tensor boundaries |     |     |     | simple |     |     |

|---------|-----|---------------------------------|-----|-----|-----|--------|-----|-----|

| op      | BS  | IF                              | OF  | FW  | FH  | KH     | KW  | op  |

| Conv    | X.B | X.C                             | Y.C | Y.W | Y.H | K.H    | K.W | MAC |

| GEMM    | X.B | X.C                             | Y.C | X.W | X.H | 1      | 1   | MAC |

| ReLU    | X.B | 1                               | Y.C | Y.W | Y.H | 1      | 1   | max |

| MaxPool | X.B | 1                               | Y.C | Y.W | Y.H | K.H    | K.W | max |

```

for batch in range(BS):

for o_feat in range(OF):

for i_feat in range(IF):

for fh in range(FH):

for fw in range(FW):

for k_y in range(KH):

for k_x in range(KW):

do simple_op

```

Listing 1. Generic CNN layer computational tensor.

```

for o_feat in range(512):

for i_feat in range(128):

for fh in range(28):

for fw in range(28):

for k_y in range(1):

for k_x in range(1):

do MAC

```

Listing 2. Computational tensor of convolutional layer  $I_1$ .

In this paper, we represent the computational tensor of every CNN layer, using a generic computational tensor and Table 3. The generic computational tensor, given in Listing 1, represents computations within every layer of a CNN architecture as a set of 7 loops, bound by generic loop bounds BS, OF, IF, FH, FW, KH and KW, and enclosing a generic simple operation *simple\_op*. To represent computations within a specific CNN layer l, the loop bounds and the simple operation in the generic computational tensor are replaced with their respective layer-specific values. For example, to represent the computations within CNN layer  $l_1$ , shown in Figure 1, the generic loop bounds OF, IF, FH, FW, KH, KW of the generic computational tensor in Listing 1, are replaced in Listing 2 with their layer-specific values:  $Y_1.C =$ 512, and  $X_1.C = 128$ , also called number of output and input features of the layer, respectively;  $Y_1.H = 28$ , and  $X_1 = 28$ , the height and width of the layer output data tensor;  $K_1.H = 1$ , and  $K_1.W = 1$ , the height and width of the layer sliding window  $K_1$ ; and the generic operation  $simple\_op$  is replaced by the layer-specific simple operation MAC. The external loop on batch size BS is omitted, assuming batch size equal to 1.

Table 3 specifies how the generic loop bounds and generic simple operations are replaced with their layer-specific values for CNN layers, performing various CNN operators. In Table 3, Column 1 lists common CNN operators; Columns 2 to 8 show how generic loop bounds *BS*, *OF*, *IF*, *FH*, *FW*, *KH* and *KW* of the generic computational tensor, given in Listing 1, are replaced by the dimensions of input layer *X*, output layer *Y* and sliding window *K* of a CNN layer; Column 9 shows how generic operator *simple\_op* of the generic computational tensor is replaced with a layer-specific

simple operator for a CNN layer. We note, that if needed, Table 3 can be customized or extended with new CNN operators or their specific implementations.

#### **B. OPS-BASED PERFORMANCE PREDICTION**

Most approaches in the literature evaluate the execution latency of a CNN as:

$$t_{OPS} = OPS/AP \tag{1}$$

where the attainable performance AP is considered equal to the peak performance of the hardware platform, APmax [OPS/s], while OPS is the total number of operations, that must be executed during the CNN inference. The value of OPS is computed as:

$$OPS = \prod_{n=1}^{N} T.dim_n * \#OPS\_enclosed$$

(2)

where  $\prod_{n=1}^{N} T.dim_n$  is a product of all computational tensor dimensions  $dim_n$ ,  $n \in [1, N]$ ;  $\#OPS\_enclosed$  is the number of OPS in a simple operation, enclosed in the loops of the layer computational tensor. For example, the total number of operations, performed by the convolutional layer, represented as a computational tensor in Listing 2, is evaluated as:  $512 * 128 * 28 * 28 * 1 * 1 * 2 \approx 102$ ,  $76 * 10^6$ , where 512 \* 128 \* 28 \* 28 \* 1 \* 1 is the product of all computational tensor dimensions and 2 indicates that every MAC operation, enclosed in the loops of the computational tensor, consists of two operations: one multiplication and one addition.

## C. ROOFLINE MODEL

The well-known Roofline Model [16] takes into account the impact of memory access on execution time. It exists in the OPS/s vs OPS/byte plane, and combines peak performance, represented as a horizontal line, with the actual bandwidth available to off-chip memory, defining a diagonal line with  $45^{\circ}$  inclination. The best-case execution time for a given kernel is defined by the operating point in the roofline. This is obtained as the intersection with the vertical line representing the kernel's Operational Intensity,  $Int(l_i)$ , defined as the ratio among OPS count and total data transferred:

$$Int(l_i) = OPS(l_i)/Traffic_{mem}(l_i)$$

(3)

For a CNN layer  $l_i$ , explained in Section III-A, the amount of data transfers, performed during the layer execution, can be estimated as:

$$Traffic_{mem}(l_i) = Size(X_i) + Size(W_i) + Size(Y_i)$$

(4)

where  $Size(X_i)$ ,  $Size(W_i)$  and  $Size(Y_i)$  stand for the amount of data (in Bytes) in input data  $X_i$ , weights  $W_i$  and output data  $Y_i$  of layer  $I_i$ . The amount of data in a data tensor T is computed as:

$$Size(T) = \prod_{n=1}^{N} T.dim_n * size of(pixel)$$

(5)

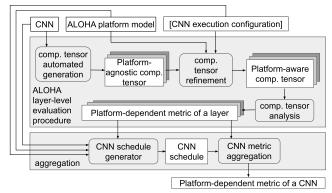

FIGURE 2. ALOHA methodology design flow.

where  $\prod_{n=1}^{N} T.dim_n$  is the total number of elements in the data tensor; sizeof(pixel) is the number of bytes, required to store one element of data tensor T.

Based on this representation, execution time is estimated according to Equation 1, with  $AP = AP_{roof}$  evaluated as:

$$AP_{roof} = min(AP_{max}, Int * bw)$$

(6)

where bw is the bandwidth to the off-chip memory.

## **IV. ALOHA METHOD**

In this section, we propose our ALOHA method. The main purpose of our method is to evaluate platform-dependent metrics, such as latency and energy consumption, related to the execution of a CNN on a specific accelerator-based target platform. The design flow of our method<sup>2</sup> is shown in Figure 2. Our method accepts as inputs:

- a CNN description, for example, in ONNX format [46], which describes a CNN as a directed computational graph, explained in Section III-A;

- a specification of the accelerator-based platform, represented using the novel ALOHA platform model, proposed in Section V;

- (optionally) a CNN execution configuration, explained in details in Section VII.

Such input is used through the phases of the proposed method:

- Phase 1: The algorithm architecture and the platformaware characteristics, specified in the platform model, are used by the ALOHA layer-level evaluation procedure, proposed in Section VI. The procedure is itself composed of several steps:

- first, as described in Section VI-A, the procedure generates a computational tensor for every layer in the CNN, depending on the layer features; we indicate this process as *Computational tensor gen*eration;

- second, as described in Section VI-B, the computational tensor is annotated considering platform features: the loops of operations and data transfers

<sup>&</sup>lt;sup>2</sup>The presented design flow corresponds to the open-source implementation of our ALOHA method, available at https://gitlab.com/aloha.eu/alohaeval

are ordered, mapped on available parallel hardware operators, and partitioned depending on the limits imposed by storage resources. In this way a new platform-aware computational tensor is obtained for every layer; we refer to this process as *Computational tensor refinement*;

- third, as described in Section VI-C, the obtained tensor is analyzed to derive accurate estimation of the metrics under evaluation; this process is referred to as Computational tensor analysis.

- Phase 2: The obtained layer-level estimations are passed as input to an aggregation module, described in Section VII, that schedules the execution of the different components on the processing elements in the platform, to deliver the final estimation of a platform-dependent metric of a CNN.

## V. ALOHA PLATFORM MODEL

When it comes to describing details of a platform, simple specifications, such as the Roofline model, fail to describe some characteristics of the implementation, or the execution dataflow, that may have a significant impact on the platform-aware metrics of a CNN. Therefore, we have defined an abstract and generalizable, yet more detailed model which enables us to capture such characteristics. In this section, we describe the main details of the proposed model. We also provide two examples of such a platform model: Table 4 and Table 5, show the platform models for the reference NEURAghe platform (see Section V-A) and the Jetson TX2 platform (see Section V-B), used in this work. The same description scheme may also apply to micro-controller based platforms, as long as the needed information regarding the working frequency and achievable performance, the local storage size and the communication resources are made available by the vendor in the related documentation. Our platform model is composed of three main elements:

- **Memory resources** (Row 2): specifies available on- and off-chip memory blocks, assigns an ID to each block, and indicates the related capacity;

- IO channels (Row 3): specifies connections that can be used to load/store input/output data to/from internal memories from/to external storage, assigns an ID to each connection, and lists the corresponding available bandwidth:

- **Processors** (Rows 4 to 16): a set of (parallel) processors, that represent the distributed heterogeneous computational resources, available on the platform, and can share the CNN workload. For the sake of brevity, in Table 4 and Table 5, we only show full processor description for the platform accelerators, and omit the full description of other processors, such as CPUs.

Every processor in our proposed platform model is composed of two main elements: a *processor description*, which describes the features of the processor, and a *computational model*, which indicates how the computational workload associated with CNN operators is deployed on the resources

TABLE 4. ALOHA platform model for NEURAghe.

| <u> </u>                         |                   |              |                   |  |

|----------------------------------|-------------------|--------------|-------------------|--|

|                                  | NEURAgh           | e Platform   |                   |  |

|                                  | ID                |              | Size              |  |

| Memory                           | 0                 | 73728 B      |                   |  |

| resources                        | 1                 |              | 3840 B            |  |

|                                  | 2                 |              | 2160 B            |  |

|                                  | 3                 |              | 97152 B           |  |

|                                  | ID                |              | vidth (BW)        |  |

| IO                               | 0                 | 0.72 GB/s    |                   |  |

| channels                         | 1                 |              | '2 GB/s           |  |

|                                  | 2                 |              | 88 GB/s           |  |

|                                  | Processor of      | lescription  |                   |  |

|                                  | id                |              | 0                 |  |

| General                          | type/sub-type     |              | r/FPGA engine     |  |

| characteristics                  | top performance   |              | 6 GOPs/s          |  |

|                                  | frequency         | 0.1          | 8 GHz             |  |

|                                  | Level             | Dimension    | Description       |  |

| Parallelism                      | level 0           | 9            | MAC matrix has    |  |

|                                  | level 1           | 10           | 9*10 MACs,        |  |

|                                  | level 2           | 4            | 4 pixels/cycle    |  |

|                                  | active power      | 3.6W         |                   |  |

| Power                            | idle power        | 1.8W         |                   |  |

|                                  | bit access to DDR | 91pJ         |                   |  |

| Overhead                         | 0.1 m             | ns           |                   |  |

|                                  | Computati         | onal Model   |                   |  |

| Loop iterating on Assigned order |                   |              |                   |  |

|                                  | OF                | Ī            | evel 1            |  |

| Loop nesting                     | IF                | 10           | evel 0            |  |

| order                            | FH                | 10           | evel 2            |  |

| and usage                        | FW                | 10           | evel 3            |  |

| _                                | KH                | le           | evel 4            |  |

|                                  | KW                | le           | evel 5            |  |

|                                  | Transfer type     | at le        | oop level         |  |

| Data transfers                   | Input Features    | 10           | evel 1            |  |

| positioning                      | Output Features   | 10           | evel 0            |  |

|                                  | Weights           | 10           | evel 1            |  |

|                                  | Transfer type     | to ch        | annel ID          |  |

| IO channel                       | Input Features    |              | 0                 |  |

| assignment                       | Output Features   |              | 1                 |  |

|                                  | Weights           |              | 2                 |  |

|                                  | Data type         | to memory ID | limited loop      |  |

| Memory                           | Input Features    | 0            | FH (Loop level 2) |  |

| assignment                       | Output Features   | 1            | OF (Loop level 1) |  |

|                                  | Weights           | 2            | OF (Loop level 1) |  |

|                                  | Level             | to loc       | pp iterator       |  |

| Parallelism                      | 0                 |              | op level 0)       |  |

| levels                           | 1                 | OF (Lo       | oop level 1)      |  |

| assignment                       | 2                 | FW (L        | oop level 3)      |  |

|                                  | Processor o       | lescription  |                   |  |

|                                  | id                |              | 1                 |  |

| General                          | type/sub-type     | CPU/Arr      | n Cortex-A53      |  |

| characteristics                  | top performance   |              | GOPs/s            |  |

|                                  | frequency         |              | 2 GHz             |  |

| jrequency 1,2 one                |                   |              |                   |  |

specified in the platform model. The *processor description* (Rows 4 to 8 and Rows 15 to 16) describes the following parameters:

- **General characteristics** (Row 5 and Row 16): this section describes general characteristics of the processor, such as unique processor identifier (id), core type, and sub-type, top performance, and frequency.

- **Parallelism** (Row 6): this section describes how many operations in parallel can be executed by each core. To be compliant with what commonly happens in accelerators, where processing capabilities can often be implemented using multi-dimensional connected structures of processing elements, hierarchically organized, the available parallelism is described as an n-dimensional grid. The user must list *n* parallel factors corresponding to the hierarchy levels exposed by the processing element structures in the platform.

- **Power** (Row 7): this section contains optional information about the power consumption of the processor described. It may report a power consumption value in the active and idle state of the processor, and an energy

TABLE 5. ALOHA platform model for Jetson TX2.

|                                         | Jetson l          | Platform       |                     |  |

|-----------------------------------------|-------------------|----------------|---------------------|--|

|                                         | ID                |                | Size                |  |

| Memory                                  | 0                 | 858            | 89934592 B          |  |

| resources                               | 1                 | j              | 131072 B            |  |

|                                         | 2                 |                | 524288 B            |  |

|                                         | ID                | Bandwidth (BW) |                     |  |

| IO                                      | 0                 |                | 20 GB/s             |  |

| channels                                | 1                 |                | 20 GB/s             |  |

| *************************************** | 2                 | 35 GB/s        |                     |  |

|                                         | Processor         | description    |                     |  |

|                                         | id                |                | 0                   |  |

| General                                 | type/sub-type     | acce           | elerator/GPU        |  |

| characteristics                         | top performance   | 66             | 6.6 GOPs/s          |  |

|                                         | frequency         |                | 1.3 GHz             |  |

|                                         | Level             | Dimension      | Description         |  |

| Parallelism                             | level 0           | 2              | MAC matrix contains |  |

|                                         | level 1           | 16             | x 2 SM x 16 blocks  |  |

|                                         | level 2           | 128            | per SM x 128 cores  |  |

| Power                                   | active power      | 120            | 15W                 |  |

| Overhead                                |                   | 0.01 ms        |                     |  |

| Computational Model                     |                   |                |                     |  |

|                                         | Loop iterating on | Ass            | igned order         |  |

|                                         | OF                |                | level 0             |  |

| Loop nesting                            | IF                | level 1        |                     |  |

| order                                   | FH                | level 2        |                     |  |

| and usage                               | FW                |                | level 3             |  |

|                                         | KH                |                | level 4             |  |

|                                         | KW                |                | level 5             |  |

|                                         | Transfer type     | at             | loop level          |  |

| Data transfers                          | Input Features    |                | level 0             |  |

| positioning                             | Output Features   |                | level 0             |  |

| 1 8                                     | Weights           |                | level 0             |  |

|                                         | Transfer type     | to             | channel ID          |  |

| IO channel                              | Input Features    |                | 1                   |  |

| assignment                              | Output Features   |                | 0                   |  |

|                                         | Weights           |                | 0                   |  |

|                                         | Data type         | to memory ID   | limited loop        |  |

| Memory                                  | Input Features    | 1              | OF (Loop level 0)   |  |

| assignment                              | Output Features   | 0              | OF (Loop level 0)   |  |

| · ·                                     | Weights           | 0              | OF (Loop level 0)   |  |

|                                         | Level             | to l           | oop iterator        |  |

| Parallelism                             | 0                 | IF (I          | Loop level 1)       |  |

| levels assignment                       | 1                 |                | Loop level 0)       |  |

|                                         | 2                 | FH, FW         | (Loop level 2, 3)   |  |

|                                         |                   | description    |                     |  |

|                                         | id                |                | 1                   |  |

| General                                 | type/sub-type     |                | RM Cortex A-57      |  |

| characteristics                         | top performance   |                | .28 GOPs/s          |  |

|                                         | frequency         | 2              | 2.35 GHz            |  |

|                                         |                   |                |                     |  |

cost per bit accessed in the global memory. This field is not needed if only latency is evaluated.

Overhead: (Row 8) optional field allowing to account for programming cycles, required to start computations on the given processor.

The *computational model* (Rows 9 to 14) depicts the following parameters:

- Loop nesting order and usage (Row 10): specifies the order, in which loop of the layer computational tensor, given in Listing 1, explained in Section III-A, are executed on a specified processor.

- Data transfers positioning (Row 11): specifies the exact positions of data transfers in the layer computational tensor. As discussed in [47], this parameter can significantly affect the layer latency and energy consumption.

- IO channels assignment (Row 12): specifies the assignment of the platform data transfer channels to input data, output data, and weights, transferred during the layer execution.

- **Memory assignment** (Row 13): specifies the assignment of the platform memories to input data, output

- data, and weights, stored on the platform during the layer execution, and poses memory constraints on the loops of the computational tensor. This parameter is specified by the assignment of the platform memories of limited sizes to the loops of the layer computational tensor. By introducing this parameter, we model the impact of limited memory resources on the layer execution. The impact of the memory hierarchy is opposed to the loop unrolling and leads certain loops of the layer computational tensor to be *tiled*: partitioned in chunks that can be handled with the data fitting those memories.

- Parallelism levels assignment (Row 14): based on the computing units available on the platform, it describes how different degrees of parallelism are used to partially unroll the convolution loops. To correctly model the execution, we associate a computational tensor loop level to each dimension of the parallel computational grid of the platform accelerator.

## A. EXAMPLE 1: DESCRIBING NEURAGHE

NEURAghe is a CNN inference accelerator that can be configured at design time with different parameterization, but we consider in this paper a setup that is implemented on Ultra96 board by Avnet, embedding a Xilinx Zynq UltraScale+ MPSoC ZU3EG A484 and a RAM Micron 2 GB LPDDR4 Memory. The memory subsystem in NEURAghe includes four defined storage spaces, defined in the *Memory* Resources slot of Table 4. The memories specified as memory 0, memory 1 and memory 2 are local to the hardware convolution accelerator available on the platform and are respectively destined to weights, activation data, and computed results, while the last one, specified as memory 3 is the off-chip memory, shared among the hardware accelerator and the generalpurpose processor. The data transfers between the global and local memories in the NEURAghe platform are handled through three separate DMA channels, transferring 8 B/cycle, described in Table 4 as IO channel 0 and 1, operating at 90 MHz, and IO channel 2 operating at 180 MHz.

The computational resources of the NEURAghe platform consist of an ARM Cortex-a53 core exploited as a general-purpose processor and a convolution-specific FPGAbased accelerator. Due to the limited space, only the platform accelerator is fully described in Table 4.

The considered configuration features a matrix of 90 MAC modules, distributed over 9 parallel input channels and 10 parallel output channels, working at 180 MHz clock frequency. Moreover, each MAC module in NEURAghe is designed to process four neighboring pixels in an input row per cycle. Table 4 models its computing resources by defining, in the *Parallelism* field, a *level*0 and *level*1 parallelism, respectively set to 9 and 10 and representing the dimensions of the computational grid, and a *level*2 parallelism, set to 4 and corresponding to the number of pixels processed per cycle. Thus the platform is able to deliver a peak performance of 129,6 GOPS/s for 16 bit CNN data precision. The platform power consumption was assessed using the Xilinx

Power Estimator tool [48], obtaining  $P_{act} = 3, 6 \text{ W}$  for the active state, and  $P_{idle} = 1, 8 \text{ W}$  for the idle state. Moreover, we have accounted for DDR energy consumption. To this aim, we have used the DRAMpower tool [49], fed with transaction traces obtained by RTL simulation. We obtained a per-bit energy contribution of  $En_{bit} = 91$  pJ/bit for a 4Gb Micron LPDDR3 memory. A typical CNN execution dataflow on the platform is described in the Computational model field. Parallelism levels are linked to their corresponding loop levels in the Parallelism level assignment section, by referring to the specific nesting order implemented in the platform, and defined in the Loop nesting order and usage section. The level 0 parallelism is exploited to unroll computations over IFs, while the level 1 parallelism, defines unrolling over OFs and level2 parallelism allows to unroll by a factor of 4 the X loop. The Memory assignment section defines how CNN data is stored in each of the storage spaces available, and how their limited size affects the execution dataflow of a CNN layer.

## **B. EXAMPLE 2: DESCRIBING JETSON**

Jetson TX2 [28] is a GPU-based platform from NVIDIA. The memory system in Jetson includes a unified 1.866-GHz DRAM memory, directly accessed and shared among all platform processors, a local GPU memory of total size 128 KB, and a shared L2 cache with a configurable size of 512 KB to 2 MB, specified in Table 5 as memory 0, memory 1, and memory 2, respectively. Transfers between the platform global memory and other platform memories are handled through separate data transfer channels, described in Table 5 as IO channels 0, 1, 2, respectively. The computational resources of the Jetson TX2 platform are composed of an NVIDIA Pascal GPU, a quad-core Dual-Core NVIDIA Denver 2 64-Bit CPU, and a quad-Core ARM Cortex-A57 MPCore. Due to the limited space, only the platform GPU is fully described in Table 5. The GPU processor of the NVIDIA Jetson TX2 platform has two Streaming Multiprocessors (SMs). Each SM has 128 1.3-GHz cores and is capable of running 2048 threads, organized in 2048/128=16 thread blocks. The parallelism within the platform GPU is specified in the field Parallelism in Table 5, as parallelism levels 0, 1, and 2 of size 2 (SMs), 16 (blocks per SM) and 128 (threads per block), respectively. The peak performance of the NVIDIA Jetson TX2 GPU reaches 666.6 GOPs/s for FP32 CNN data precision (see field General characteristics in Table 5). Execution of a CNN on the Jetson TX2 platform is typically performed using the TensorRT DL framework [50], provided by NVIDIAs as an official DL framework for the platform. The TensorRT framework exploits the parallelism within the CNN layers, as specified in Loop nesting order and usage field in Table 5. As specified in field *Memory assignment*, during the CNN execution, the framework uses the global platform memory to store the output data and weights of CNN layers, and the shared GPU memory to store input data of CNN layers. When executed on the Jetson TX2 platform, computations within the CNN layers are limited by the sizes of the platform memories, as specified in field *Memory* assignment in Table 5.

## **VI. ALOHA EVALUATION PROCEDURE**

In this section, we provide details about the ALOHA evaluation procedure. Our method ensures fast, yet accurate, evaluation of the CNN layers performance. Unlike other analytical methods with a similar level of abstraction, such as the Roofline model or OPS-based evaluation, discussed in Section II, our evaluation procedure captures the following important platform-aware factors, that affect platform-dependent metrics of every CNN layer executed on heterogeneous hardware platforms:

- repeated transfers of the layer input data and weights from the platform global memory to the local memories of the platform processors occur when the local platform memory, allocated to store the layer data and weights cannot accommodate all the data and weights at once. Memory size also affects the amount of output data transferred from the local memory to the global one. The repetitive transfers cause additional time and energy overheads during the CNN layer execution;

- occupancy/rounding effect, i.e., a waste of computational power, caused by inefficient exploitation of the parallelism available in the platform, by the parallel computations to be carried out within a CNN layer [47]. Such waste is typically measured using wasted computational cycles, or partial processor occupancy, resulting in reduced performance of the platform computational resources [47];

- separate bandwidth ceilings reflect communication overheads, caused by an uneven distribution of the CNN layer data (input data, output data, and weights) over platform memories and data communication channels. Typically, the memory bandwidth of the platform is described by the peak memory bandwidth, which accounts for a high utilization of all data communication channels, available on the platform. However, in practice, not all data communication channels, available on the platform, are (efficiently) utilized, which leads to additional time overheads during the CNN layer execution.

Considering the aforementioned factors allows our method to achieve higher accuracy in evaluating platform-aware metrics of a CNN layer, compared to other analytical methods with a similar level of abstraction. The evaluation procedure involves three main phases:

- Computational tensor generation. This phase generates a representation of a CNN layer, annotated with an operator, input, and output data formats and weights, as a computational tensor, explained in Section III-A. It enables for explicit specification of the parallelism available within the CNN layer. The description of its functioning is placed in Section VI-A.

- Computational tensor refinement. In this phase, the generated platform-agnostic layer computational tensor

- is enriched with platform-aware parameters of the ALOHA platform model, explained in Section V, and transformed into a platform-aware computational tensor. A detailed description of the steps performed in this phase, and of their effects, is given in Section VI-B.

- Computational tensor analysis. This phase involves analysis of the platform-aware computational tensor and final estimation of the platform-dependent metric of interest. Further description is given in Section VI-C.

To illustrate the phases of our evaluation procedure, we use as an example the convolutional layer  $l_1$ , shown in Figure 1, and explained in Section III-A, executed on the NEURAghe platform, represented as the ALOHA platform description in Table 4.

#### A. COMPUTATIONAL TENSOR GENERATION

In this phase, the ALOHA evaluation procedure represents the CNN layer as a 6-dimensional computational tensor, explained in Section III-A. To generate the layer computational tensor, the ALOHA method uses the generic CNN layer representation, given in Listing 1 and Table 3. For example, for the CNN layer  $l_1$ , shown in Figure 1, and explained in Section III-A, the ALOHA procedure generates the CNN layer computational tensor, provided in Listing 2.

## B. COMPUTATIONAL TENSOR REFINEMENT

In this phase, the ALOHA evaluation procedure enriches the computational tensor of the CNN layer with platform-aware parameters of the ALOHA platform model, explained in Section V. The computational tensor refinement is performed in four steps (see Step 1 to Step 4 below). Steps 1 to 4 subsequently apply specific transformations to the computational tensor of the CNN layer. In this section, we show an example where the platform-agnostic computational tensor, given in Listing 2, explained in Section III-A, is refined with platform-aware details of the NEURAghe platform, represented using the ALOHA platform description in Table 4.

- Step 1: Apply loop nesting order and usage to the order of computational tensor loops. This step makes lines 1 and 2 in Listing 2 to swap places, resulting in Listing 3;

- Step 2: Apply parallelism level assignment to every computational tensor loop, unrolled over a dimension of a parallel computational grid. During this step, an indented loop *par\_\**, representing parallel computations, is inserted in the nested structure, according to the *Parallelism level assignment* field. The consequence of this action is that the number of iterations of the new couple of loops is rounded over the corresponding computational grid dimension. For example, the level 0 parallelism of size 9, shown in Table 4, and assigned to the IF loop of the computational tensor, causes the insertion of loop *par\_0* with 9 iterations in Listing 4 (line 2), and rounding of the IF loop (line 1) to roundup(128/9) = 15 iterations. Analogously, the level 1 parallelism of

- size 10, shown in Table 4, and assigned to the OF loop of the computational tensor, causes the insertion of loop  $par_1$  with 10 iterations in Listing 4 (line 4), and rounding of loop OF (line 3) to roundup(512/10) = 52 iterations.

- Step 3: Introduce data transfers, i.e., explicitly specify the transfer of the layer input data, output data, and weights in the layer computational tensor. Every data transfer is assigned to a specific loop in the computational tensor, as described in the data transfer positioning field of the platform computational model, and is represented as a line  $action(data\_bytes, mem_i, ch_i)$ , where  $action \in (load, store)$  specifies whether the data is transferred from the main memory to the local processor memory (action = load), or from the local processor memory to the main platform memory (action =store). If action = load, the data transfer is placed before the computations within the assigned loop are performed. If action = store, the data transfer is placed after the computations within the assigned loop are performed; data\_bytes specifies the amount of data (in bytes) transferred during the data transfer action. The data bytes parameter is assessed for every op/data type, using specific properties of the CNN layer and the layer computational tensor; mem; specifies the platform memory, where data is accumulated;  $ch_i$  specifies the data transfer channel, used for transfer of the data. For example, in Listing 5, this step leads to the insertion of line 2, where input data of the CNN layer of size 9 \* 28 \* 7 \* 4 \* 2 bytes is loaded from the device main memory into the processor local memory mem<sub>0</sub> through data communication channel  $ch_0$ . How to evaluate data transfer size is further detailed in Equation 7, introduced in the following phase, describing the Computational tensor analysis.

- Step 4: Pose memory constraints onto computational tensor loops. During this step, the evaluation procedure checks every loop, associated with a limited platform memory, as specified in the *Memory assignment* field of the platform model. If the utilization of the platform memory within the loop violates the memory constraint, the loop is tiled to avoid the violation. For example, as specified in Table 4, the OF loop of the computational tensor is limited by the local memory mem<sub>1</sub> of size 163840 bytes. In Listing 5, the layer tries to accumulate 815360 bytes in memory  $mem_1$  (line 13), where 815360 > 163840, and thus, Listing 5 violates a constraint, placed by memory  $mem_1$  on the OF loop. This causes introduction of additional loop out\_tile (line 1 in Listing 6) with 6 iterations, and reduction of the OF loop (line 6 in Listing 6) to 52/6 = 9 iterations. In Listing 6, the layer stores 9 \* 10 \* 28 \* 7 \* 4 \* 2 = 141120 bytes < 163840 bytes of output data in memory  $mem_1$  at each iteration of loop *out tile*, and thus, does not violate the memory constraint, placed by memory mem1 on the OF loop.

```

for i_feat in range(128):

for o_feat in range(512):

for fh in range(28):

for fw in range(28):

for k_y in range(1):

do MAC

```

Listing 3. Step 1. Loops nesting order and usage.

```

for i_feat in range(15):

for par0 in range(9):

for o_feat in range(52):

for par1 in range(10):

for fh in range(28):

for fw in range(7):

for par2 in range(4):

for k_y in range(1):

do MAC

```

Listing 4. Step 2. Parallelism levels assignment.

Listing 5. Step 3. Data transfers introduction.

Listing 6. Step 4. Limits posing (tiling).

## C. COMPUTATIONAL TENSOR ANALYSIS

In this phase, the ALOHA evaluation procedure analyses the platform-aware computational tensor, to estimate the total number of operations and data transfers, performed during the execution of a CNN layer. The total number of operations is computed using Equation 2 in Section III-B. According to Equation 2, the total number of operations  $OPS_{re}$ , performed by the refined CNN layer computational tensor, shown in Listing 6, is computed as:  $OPS_{re}^3 = 6 * 15 * 9 * 9 * 10 * 28 * 7 * 4 * 1 * 1 * 2 \approx 110, 07 * 10^6$ .

We note, that this number of operations does not match the total number of operations  $OPS_{th} = 102, 76*10^6$ , computed in Section III-A for the platform-agnostic CNN layer computational tensor, shown in Listing 2. The difference between  $OPS_{re}$  and  $OPS_{th}$  estimations occurs, because of an imperfect distribution of the layer computations over the platform processors. As a result, the CNN layer, distributed over the parallel computational resources of the platform (Listing 6), wastes some of the computational cycles, i.e., suffers the rounding effect. The refinement of the layer computational tensor with platform details enables for consideration of the rounding effect and therefore enables for more precise representation of the CNN layer execution on the target platform.

Analogously, considering the platform-aware computational tensor allows assessing the actual amount of memory transfers, impacting the layer's operational intensity. Instead of using Equation 5, which defines the theoretical transfers based on data tensor dimensions, under the assumption that all of the data can be transferred at once to local memories and made available throughout the entire computation, the ALOHA method considers how the specific nesting structure implemented impacts the actual memory traffic.

The amount of data transferred for every data tensor can be evaluated as:

$$Size_{re}(T) = \prod_{n=1}^{N} T.dim'_{n} * sizeof(pixel) * iterations_{tl}$$

(7)

where, if one of the  $T.dim_n$  dimensions of data tensor T is subject to partitioning among multiple loops, we define as  $T.dim'_n$  the dimension that is handled in convolution loops internal to the transfer level tl, which is subject to a certain number of *iterations*<sub>tl</sub>, based on loop nesting structure.

Given the IO channel assignment, the ALOHA model evaluates the operational intensity over single available channels, exploiting Equation 3, where the OPS count is evaluated in details, considering rounding effects and tiling according to Listing 6, and the traffic value accounts for repeated transfers, exploiting Equation 7.

At this point, it is possible to use an approach inspired by the Roofline model, but turning Equation 6 into:

$$AP_{ALOHA} = min(AP_{max}, Int_{ch0} * bw_{ch0}, \dots, Int_{chn} * bw_{chn})$$

(8)

Considering  $AP = AP_{ALOHA}$  in Equation 1, the execution time is evaluated as:

$$t_{ALOHA} = OPS_{re}/(AP_{ALOHA}) + ov (9)$$

where known programming overhead, acting as a fixed offset ov, is added to the predicted value.

## **VII. CNN METRIC AGGREGATION**

In this section, we present our CNN metric aggregation module. As explained in Section VI, the CNN metric aggregation module accepts as inputs estimations of the platform-dependent metrics of CNN layers and aggregates

$<sup>^3</sup>$ Description in Listing 6 is simplified for the reader. It does not present some details, e.g. in the last iteration of the loop at line 2, the loop at line 6 stops as soon as roundupOF = 520 OFs have been processed.

them to deliver the final estimation of a platform-dependent metric of a CNN, such as CNN latency, CNN energy, and CNN throughput.

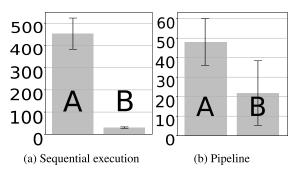

Despite systems with multiple accelerators being hardly available in the embedded domain, some research efforts have demonstrated that such a design technique can be useful [51], [52]. Thus our aggregation methodology enables the estimation to take into account an arbitrary number of processing elements. We do not account for contention on the off-chip memory, since previous experiments have shown that the effect of this issue is limited. References [51] shows this for the case of multiple NEURAghe instances insisting on the same DDR memory. We also assume, as in most of the approaches in the literature, communication with the host to be asynchronous, thus we do not consider the host CPU intervention to become a bottleneck.

Furthermore, in embedded systems, sensors are usually monitored with a specific frequency that is known at design time. Thus we assume input samples to be processed as soon as possible, as allowed by the throughput estimated by the method. In the case of variable sampling frequency, we assume design constraints to be defined according to the maximum rate of input samples and lower instant rates to be exploited for energy reduction using clock frequency scaling.

Along with the CNN, the platform specification, and the per-layer estimations of platform-dependent metrics, discussed in Section IV, the aggregation module accepts an optional *CNN execution configuration* input. This input consists of two optional parameters, characterizing the execution of a CNN on a target platform:

- distribution of CNN operators over the target platform processors;

- 2) exploitation of task-level (pipeline) parallelism, available among layers of a CNN.

The distribution of CNN operators specifies how the CNN layers should be distributed over heterogeneous processors in a target platform, prospectively dedicated to different sets of operators (e.g. on an FPGA-based platform, where only some of the CNN operators can be executed on the FPGA, and the rest of the CNN operators are executed on the platform CPUs). Formally, we define this parameter as a set of tuples  $op\_dist = \{(op, proc\_type)\}, \text{ where } op \text{ is a CNN operator}$ (such as Convolution or Pooling) and proc\_type is the type of a platform processor (e.g. CPU or GPU). For example, a set of tuples {(conv, accelerator), (gemm, CPU)} specifies that during the CNN execution, computations within every CNN layer l with l.op = conv are performed only on the platform accelerator, and the computations within every CNN layer lwith l.op = gemm are performed only on the platform CPUs. If for a CNN operator op, no processor types are specified in the distribution op\_dist, the aggregation module assumes, that every layer, performing operator op, can be executed on every processor, available on the target platform.

The exploitation of task-level (pipeline) parallelism specifies if a CNN is executed sequentially or as a pipeline. When a CNN is executed sequentially, only one of the CNN layers is executed at every moment in time. This type of CNN execution is typical for the majority of widely used DL frameworks such as PyTorch [37] or TensorFlow [38]. The execution of a CNN as a pipeline is an alternative to the sequential CNN execution. When a CNN is executed as a pipeline, several CNN layers can be executed in parallel, processing different inputs of a CNN. Execution of a CNN as a pipeline enables for higher throughput of CNNs, executed on heterogeneous target platforms [39], [40], and thus, it should be taken into account. Formally, we define the exploitation of task-level (pipeline) parallelism as a parameter  $pipeline \in \{true, false\}$  with default value pipeline = false. If pipeline = true, a CNN is executed as a pipeline, otherwise the CNN is executed sequentially.

The CNN execution configuration is accepted as input by the CNN schedule generator module of the CNN metric aggregation module. The CNN schedule generator generates a schedule J for the input CNN. Schedule J assigns each layer  $l_i \in L$  of the CNN a starting time  $s_i \geq 0$  and a processor  $PE_i, j \in [1, M]$  to be executed on. Currently, our CNN schedule generator can generate two types of schedule: 1) a sequential schedule, typical for CNNs, executed by widely used DL frameworks. This type of schedule is generated for CNN execution configurations with *pipeline* = *false*; 2) a pipeline schedule, proposed in [39], where a CNN is partitioned into M partitions, mapped onto M processors of the target platform, and all M CNN partitions are executed in parallel. This type of schedule is generated for the CNN execution configurations with pipeline = true. Additionally, if needed, one can extend our proposed CNN schedule generator or replace it with an alternative.

To generate a sequential schedule, our aggregation module uses Algorithm 1. Algorithm 1 accepts as inputs: 1) a CNN; 2) set of processors  $PE = \{PE_1, PE_2, \dots PE_M\}$ , available on the target platform; 3) a distribution of the CNN operators over the target platform processors op\_dist; 4) a set of per-layer latency estimations  $\{t(l_i, PE_i)\}, i \in [1, L], j \in$ [1, M]. As output, Algorithm 1 provides a CNN schedule, represented as a set of pairs  $(s_i, PE_i)$ , where  $s_i$  is the starting time of a layer  $l_i \in L$ ;  $PE_i \in PE$  is a processor of the target platform. In Line 1, Algorithm 1 defines an empty schedule J and sets current starting time s to 0. In Lines 2 to 17, Algorithm 1 assigns time  $s_i \ge 0$  and processor  $PE_i \in PE$  to every layer  $l_i \in L$  of a CNN. In Lines 3 to 9, Algorithm 1 defines list of processors PEsuitable, suitable for execution of layer  $l_i$ . If operator op, performed by layer  $l_i$  is specified in the distribution op\_dist, list of suitable processors PE<sub>suitable</sub> is defined in Lines 5 to 7 as a list of all processors, that support operator op. Otherwise,  $PE_{suitable}$  is defined in Line 9 as a list of all processors, available on the platform. In Lines 10 to 14, Algorithm 1 selects processor  $PE_i$  from the list of suitable processors  $PE_{suitable}$ , such that execution of layer  $l_i$  on the processor  $PE_i$  leads to the smallest latency  $t(l_i, PE_i)$  of layer  $l_i$ . In Lines 15 to 17, Algorithm 1 assigns time  $s_i = s$  and processor  $PE_i$  to the layer  $l_i$  (Line 15) and increases starting time s by the latency  $t(l_i, l_i)$  of layer  $l_i$ ,

#### Algorithm 1: Sequential Schedule Generation **Input:** CNN(L, E), PE, $op\_dist$ , $\{t(l_i, PE_i)\}$ **Result:** CNN schedule *J* 1 $J = \emptyset$ ; s = 0; 2 for $i \in [1, |L|]$ do $PE_{suitable} = \emptyset;$ if $\exists (op, proc\_type) \in op\_dist : op = l_i.op$ then 4 5 **for** $(l_i.op, proc\_type) \in op\_dist$ **do for** $PE_i \in PE : PE_i.type = proc_type$ **do** $PE_{suitable} = PE_{suitable} + PE_i;$ 7 8 $PE_{suitable} = PE;$ 9 $PE_i = PE_{suitable}.pop();$ 10 while $PE_{suitable} \neq \emptyset$ do 11 $PE_k = PE_{suitable}.pop();$ 12 if $t(l_i, PE_k) < t(l_i, PE_i)$ then 13 $PE_i = PE_k;$ 14 15 $s_i = s$ ; $J = J + (s_i, PE_i);$ 16 $s = s + t(l_i, PE_i);$ 17 18 return J

executed on processor  $PE_j$ . Finally, in Line 18, Algorithm 1 returns sequential schedule of the input CNN.

To generate a pipeline schedule, our aggregation module uses the heuristic algorithm, proposed in [39]. As explained above, the pipeline schedule can affect the CNN throughput. Our proposed CNN metric aggregation module captures the impact of the CNN schedule on the CNN throughput by considering the CNN schedule during the CNN throughput estimation (see Equation 11 explained below).

The CNN schedule, generated by the CNN schedule generator, is accepted as input by the CNN metric aggregation sub-module, along with per-layer CNN metric evaluations. The CNN metric aggregation sub-module, uses Equation 10, Equation 11 and Equation 12 to estimate CNN latency  $t_{CNN}$  (in seconds), CNN throughput  $Th_{CNN}$  (in frames per second) and CNN energy cost  $En_{CNN}$  (in Joules), respectively.

$$t_{CNN} = s_{|L|} + t(l_{|L|}) - s_1$$

$$Th_{CNN} = \begin{cases} 1/\max_j \sum_{(s_i, PE_j) \in J} t(l_i) & ifpipeline \\ 1/t_{CNN} & otherwise \end{cases}$$

$$En_{CNN} = \sum_{(s_i, PE_j) \in J} t * P_{act} + t_{idle} * P_{idle} + b_{acc} * En_{bit}$$

$$(12)$$

In Equation 10, the total CNN latency is computed as the difference between end time  $s_{|L|} + t(l_{|L|})$  of the last CNN layer  $l_{|L|}$  and the start time  $s_1$  of the first CNN layer  $l_1$ ; Latency  $t(l_i)$  of CNN layer  $l_i$  is estimated by the ALOHA per-layer evaluation procedure, proposed in Section VI.

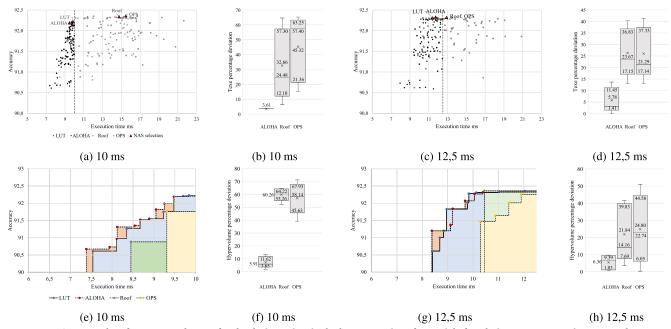

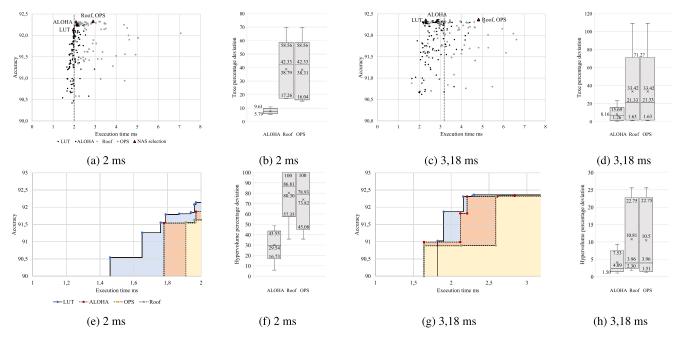

In Equation 11, the CNN throughput is computed. If a CNN is executed as a pipeline, its throughput is estimated as 1, divided on time  $\max_j \sum_{(s_i, PE_j) \in S} t(l_i)$ , required to execute CNN on processors  $\{PE_j\}, j \in [1, M]$  of the target platform, where  $\sum_{(s_i, PE_j) \in S} t(l_i)$  is time (in seconds), taken by processor  $PE_j$  to execute all CNN layers  $\{l_i\}$ , mapped on this processor. If a CNN is executed sequentially, its throughput is computed as  $1/t_{CNN}$ , where  $t_{CNN}$  is the CNN latency, computed using Equation 10.